Transforming interactions in ways you've never imagined

# i.MX 8 Family of Applications Processors

Built with advanced media processing, secure domain partitioning and innovative vision processing, the i.MX 8 applications processor family will revolutionize multiple display automotive applications, industrial systems, vision, HMI and single-board computers.

# TARGET APPLICATIONS

- Automotive infotainment—instrument cluster, head unit, heads-up display (HUD), rear seat entertainment and full digital electronic cockpit (eCockpit)

- Advanced industrial human machine interface (HMI) and control

- Single-board computers

- Home/Building

# **MULTIPLE SYSTEMS, ONE PROCESSOR**

- Easily combine multiple systems into one Build multiple platforms with multiple operating systems on a single i.MX 8 processor. The i.MX 8 full-chip hardware-based virtualization, system MMU, resource partitioning and split GPU and display architecture enable faster time-to-market and lower cost than simple hypervisor techniques alone.

- Securely change hardware partitions at run time Applications can 'sand-box' operations by moving hardware IP such as GPU, display or peripherals to multiple firewalled domains at run time.

- Secure your system with advanced programmable security Top-of-the-line security from first boot to securing with the latest cryptography standards (AES, flashless SHE, elliptical curve cryptography, key storage).

- Improve your system reliability with FDSOI Built using 28 nm FDSOI, the i.MX 8 applications processor enables improved MTBF and decreases soft error rates due to FDSOI's inherently high immunity to alpha particle flux.

## THE NEW USER INTERACTION PARADIGM

- Create advanced vision-based HMI systems

High-performance end-to-end vision processing for vision-based assistance, tracking and object detection.

- ▶ 360-degree expanded sight Utilize multi-camera input, digital stitching and VX vision extensions and provide a view from any angle.

- Multi-domain voice recognition

Utilize the ARM® Cortex®-A72 and Cortex-M4F cores as well as the HiFi 4 DSP\* for advanced echo cancellation, key word detection and speech recognition for hands-off interaction.

## **MULTI-DISPLAY & MULTI-DOMAIN FUNCTIONALITY**

• Four screens of independent content

Develop innovative, multi-screen platforms through the ability to drive up to four 1080p screens with independent content, or a single 4K screen.

- Ensure your display stays up and correct SafeAssure® ASIL-B ready hardware protects critical visual information with fail-over-capable quality of service to any display.

- Offload time-critical tasks

Utilize dual Cortex-M4F cores for time-critical tasks such as backup camera display, audio control and general system monitoring and wakeup.

## THE SCALABLE PLATFORM OF CHOICE

- Comprehensive software support Android<sup>™</sup>\*, Linux<sup>®</sup>\*, QNX, Green Hills<sup>®</sup>, DornerWorks XEN and FreeRTOS<sup>™</sup>

- Automotive, industrial, consumer qualified

Auto (-40 °C to 125 °C Tj), industrial (-40 °C to 105 °C Tj), consumer (-20 °C to 105 °C Tj)

#### PIN AND POWER COMPATIBLE

Highly scalable design options allow a single platform to cover multiple products. Pin- and power-compatible packages (in 0.75 and 0.65 pitch) allow a single PCB platform and utilize different i.MX 8 processors as product needs dictate.\*

### EARLY DEVELOPMENT ACCESS

The i.MX 8 multi-sensory evaluation kit (MEK) is available now to prototype i.MX 8 and i.MX 8X systems. Contact your NXP sales representative for details.

## i.MX 8 FAMILY—DIFFERENTIATED FEATURES

| Feature               | i.MX 8QuadMax          | i.MX 8QuadPlus      | i.MX 8Quad          |

|-----------------------|------------------------|---------------------|---------------------|

| ARM <sup>®</sup> Core | 2 x ARM<br>Cortex®-A72 | 1 x Cortex-A72      | -                   |

| ARM Core              | 4 x Cortex-A53         | 4 x Cortex-A53      | 4 x Cortex-A53      |

| ARM Core              | 2 x Cortex-M4F         | 2 x Cortex-M4F      | 2 x Cortex-M4F      |

| DSP Core              | HiFi 4 DSP             | HiFi 4 DSP          | HiFi 4 DSP          |

| GPU                   | 2 x GC7000XSVX         | 2 x GC7000Lite/XSVX | 2 x GC7000Lite/XSVX |

| PCIe 3.0              | 1 x PCIe (2-lane)*     | 1 x PCIe (1-lane)   | 1 x PCIe (1-lane)   |

\*2-lane PCIe can act as 2 x 1-lane PCIe

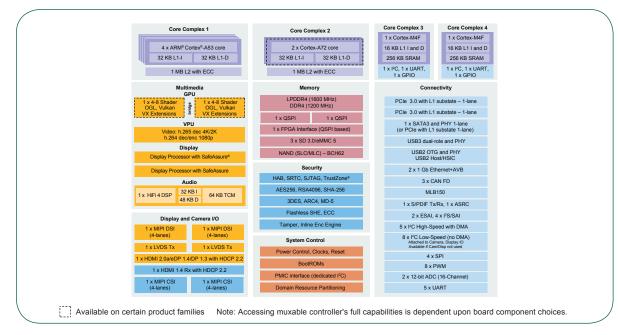

## i.MX 8 FAMILY BLOCK DIAGRAM

#### www.nxp.com/iMX8

NXP, the NXP logo and SafeAssure are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, Cortex and TrustZone are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. © 2015–2016 NXP B.V.

Date of Release: October 2016 Document Number: IMX8FAMFS REV 1

#### i.MX 8 FAMILY—COMMON FEATURES

| Feature               | Description                                                                        | Feature             | Description                                                             |

|-----------------------|------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------|

| DRAM                  | 64-bit LPDDR4/<br>DDR4                                                             | QuadSPI             | 2 x QuadSPI<br>(1 x OctoSPI)                                            |

| VPU                   | 4K h.265 dec,<br>HD h.264 enc                                                      | USB with PHY        | 1 x USB 3.0,<br>2 x USB 2.0                                             |

| Display<br>controller | 2 x DCs with<br>WARP and failover                                                  | SPDIF Tx/Rx         | 1 x                                                                     |

| MIPI DSI              | 2 x 4-lane MIPI<br>DSI                                                             | SD and<br>eMMC      | 3 x SD 3.0/eMMC 5.0                                                     |

| MIPI CSI              | 2 x 4-lane MIPI<br>CSI                                                             | NAND                | 1 x – BCH62                                                             |

| LVDS                  | 2 x LVDS                                                                           | FPGA<br>Interface   | Yes - 4 x data lane,<br>1 x Clock                                       |

| HDMI, eDP,<br>DP Tx   | 1 x HDMI 2.0a/<br>eDP 1.4/DP 1.3<br>HDCP 2.2                                       | I <sup>2</sup> C    | 5 x l <sup>2</sup> C (high speed) +<br>8 x l <sup>2</sup> C (low speed) |

| HDMI Rx               | 1 x HDMI 1.4 Rx<br>HDCP 2.2                                                        | SPI                 | 4 x SPI                                                                 |

| SATA 3.0              | 1 x SATA 3.0<br>(1-lane) or PCle<br>(1-lane)*                                      | Audio<br>Interfaces | 2 x ESAI, 5 x<br>I²S/SAI                                                |

| Security              | HAB, DPA, enc/<br>dec, flashless<br>SHE inline DDR<br>encryption,<br>4 tamper pins | Keypad              | 1 x                                                                     |

| CAN                   | 3 x CAN FD                                                                         | MPEG-2 T/S          | 2 x MPEG-2 T/S                                                          |

| MLB                   | 1 x MLB 150/<br>MLB25                                                              | ADC                 | 2 x 12-bit<br>(16 channels each)                                        |

| Ethernet              | 2 x Gigabit<br>Ethernet with AVB                                                   | UART                | 5 x UART<br>1 x UART per ARM®<br>Cortex®-M4F                            |

\*The SATA 3.0 controller can be used as PCIe (1-lane). This is in addition to the other PCIe controllers. Note: Accessing muxable controller's full capabilities is dependent upon board component choices.